文|半导体产业纵横

MRAM是下一个黑马赛道。

IEDM是全球最大的半导体器件技术与工艺技术国际学术会议,于2024年12月11日闭幕。这次也有不少值得关注的讲座(研究论文)。在本文中,我们将介绍与磁存储器(MRAM)相关的三项研究成果。

其中之一是铠侠和 SK hynix 的联合研究成果,这是关于使用交叉点结构的 64 Gbit 高容量 STT(自旋注入扭矩)——MRAM原型的演示。其余两项是三星电子的研究成果,一项是兼容14nm代CMOS逻辑并兼容汽车1级(AG1)的嵌入式STT-MRAM的开发成果,另一项是关于与 8nm 代 CMOS 逻辑兼容的嵌入式 STT-MRAM 的研究成果报告。

铠侠和SK海力士:64Gbit STT-MRAM

首先介绍一下铠侠和SK海力士联合生产的交叉点结构的64Gbit STT-MRAM的概况。这里,交叉点结构是其中整个存储单元容纳在字线和位线交叉的微小区域(交叉点)中的结构。通过在交叉区域中堆叠存储元件和选择器(两端单元选择元件)来构造一个存储单元。除了 3D NAND 闪存技术之外,理论上可以实现最高密度的存储单元阵列。

铠侠和SK海力士联合原型的交叉点结构存储单元阵列从下到上由字线层、选择器、中间电极层、磁隧道结(MTJ,存储元件)和位线层组成字线和位线的半节距短至20.5nm。存储单元面积极小,仅为 0.001681 μm 见方。

选择器的材料是砷(As)掺杂的二氧化硅(SiO2)。这是SK海力士长期以来一直在研究的一种材料,作为交叉点存储器的选择器。MTJ的细节尚未公开(隧道绝缘膜是氧化镁:MgO)。存储单元阵列的最小单位是8Mbit(4K行×2K列)。

使用透射电子显微镜 (TEM) 观察到的原型存储单元阵列的横截面图像。左边是在字线和位线方向上观察到的横截面图像。最上面的存储单元阵列下方是 CMOS 逻辑外围电路。右侧的图像是沿字线方向拍摄的截面图像。这里,“1S1M”是指由“1个选择器(S)和1个磁隧道结(M)”构成的存储单元。摘自铠侠和SK海力士在IEDM 2024上发表的论文

存储单元阵列将形成在14nm节点CMOS逻辑外围电路的正上方。该结构被称为“CUA(CMOS Under Array)”,可以节省硅芯片面积。通过三维层压结构实现的大容量是交叉点结构的特征,但在本演示中并未采用。假设重点是增加单层的容量。原型MRAM的读取时间为6ns至10ns,写入时间相当短,为15ns至30ns。

原型 64Gbit STT-MRAM 硅芯片的显微图像。硅芯片尺寸未公开。摘自铠侠和SK海力士在IEDM 2024上发表的论文

在存储单元制造中,关键是在不损坏 MTJ 的情况下缩小间距。通过使用离子束蚀刻(IBE)进行图案加工,并在不降低性能的情况下保持MTJ的低纵横比,可以抑制损坏(主要是短路缺陷)。

原型存储单元中的读取干扰直到106个读取周期才发生(未执行数据重写)。已确认重写循环寿命可达 10 次立方循环。

工业和汽车应用MRAM所需规格的差异

接下来我们来报道一下三星的研究成果。第一个是开发与汽车 1 级 (AG1) 兼容的嵌入式 MRAM。我们设想将其应用于汽车微控制器的程序存储存储器和 SoC 的工作存储器。制造工艺与 14nm 节点 FinFET 逻辑兼容。它在逻辑制造方面已经是一项成熟的技术。

半导体产品按用途分为:民用(一般消费设备)、工业用途(制造/组装/检查设备)、汽车用途(汽车电子设备)和太空/军事用途。每个应用程序都需要不同的操作环境和可靠性级别,通常按照上面列出的顺序变得更加严格(民用最宽松,太空/军事最严格)。

就量产产品而言,要求最高的是汽车用产品。即使是相同的量产产品,与工业产品相比,高温侧的工作温度范围更宽,不良率低一到两个数量级。

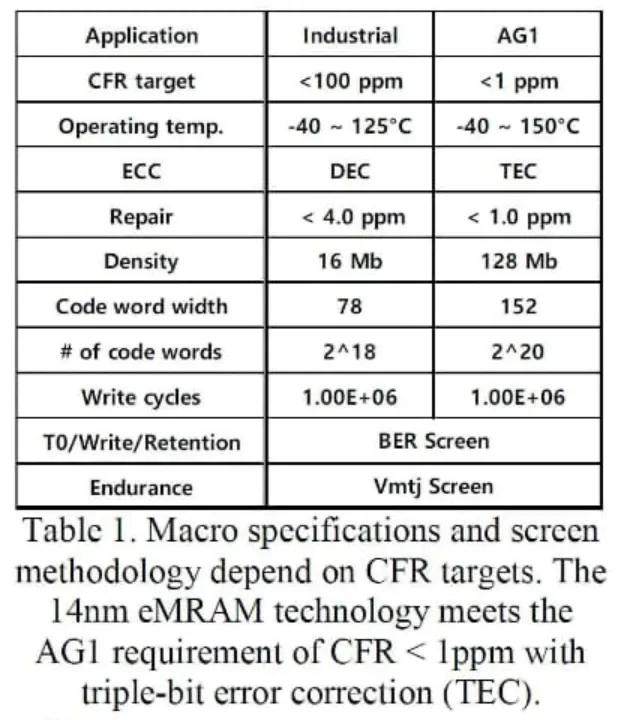

工业嵌入式 MRAM 宏和汽车嵌入式 MRAM 宏所需规格的差异。汽车应用需要低芯片故障率、高温运行、低修复率、更强的纠错(ECC)功能和更大的存储容量。摘自三星在 IEDM 2024 上发表的论文

定义汽车半导体集成电路可靠性等级的通用标准“AEC-Q100”根据工作温度范围定义了四个等级(0级至3级:AG0至AG3)。在这两种情况下,低温都相同为-40℃。高温方面,AG0在+150℃最严格,其次是AG1在+125℃,AG2在+105℃,AG3最宽松,在+85℃。

三星宣布推出支持 AG1 的嵌入式 MRAM。原型的测量数据证实其工作温度可达 +150°C。该温度本身对应于 AG0。然而,由于该产品在规格上有一定的余地,因此它似乎正在推广AG1,后者的级别要低一级。

令我惊讶的是AG1的温度范围对于程序存储存储器(三星将其描述为“eFlash型”或“Flash型”)和工作存储器(三星将其描述为“nvRAM型”)来说,具有明显的矛盾特性。尤其是“nvRAM型”的性能提升非常显著。

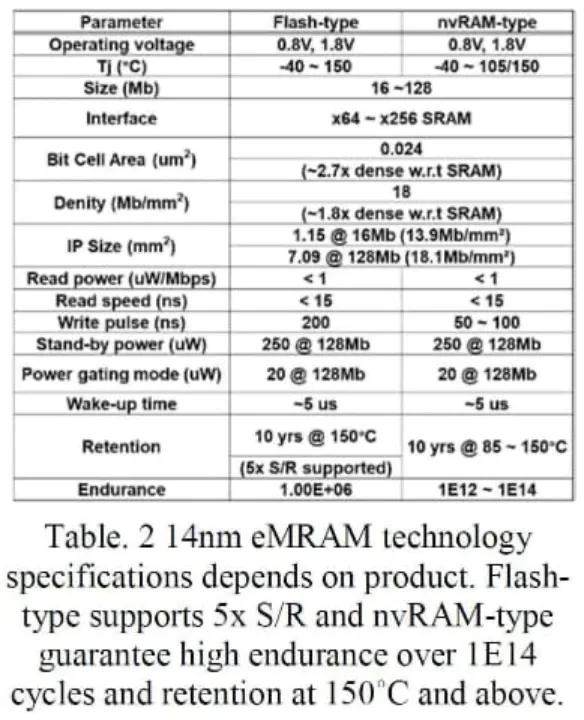

所开发的eMRAM的主要特性(根据产品规格)。左边是用于程序存储的eMRAM(Flash型),右边是用于工作区的eMRAM(nvRAM型)。摘自三星在 IEDM 2024 上发表的论文

闪存类型拥有 28nm FD SOI 逻辑的商业化记录。Flash类型为14nm节点,符合AG1标准,重写周期寿命为106个周期,150℃下数据保存期为10年,足以满足程序存储。此外,它还具有耐热性,可进行 5 次回流焊。

14nm 节点 AG1 兼容 nvRAM 类型具有极长的重写周期寿命,可达 10 至 12 个功率周期至 10 至 14 个功率周期。它的使用方式似乎与普通 DRAM 几乎相同。在85℃至150℃温度下数据保存期长达10年。事实上,它实现了 10 年的数据保留期和 10 次方的重写寿命和 12 次方的重写寿命,这着实令人惊讶。

与 8nm FinFET 逻辑兼容的汽车嵌入式 MRAM 技术

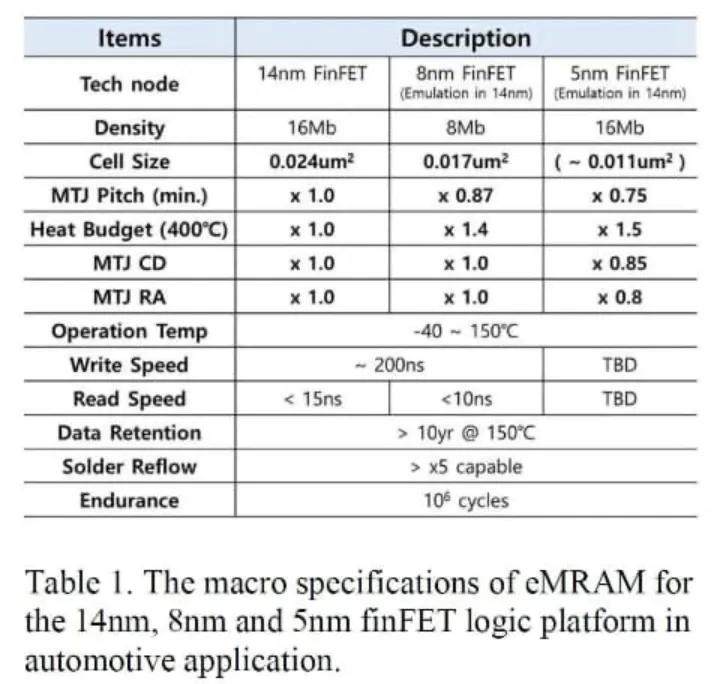

三星宣布的第二个与嵌入式MRAM(eMRAM)相关的开发成果是一种与从14nm节点进一步细化的CMOS逻辑兼容的车载eMRAM技术(讲座/论文第11-4号)。我们开发了与使用 8nm 节点 FinFET 的 CMOS 兼容的 eMRAM 技术。此外,我们还研究了与 5nm 节点使用 FinFET 的 CMOS 逻辑兼容的 eMRAM 技术。

8nm FinFET 兼容 eMRAM 具有 0.017 μm 见方的小存储单元面积。兼容14nm逻辑的eMRAM单元尺寸为0.024μm见方,因此单元面积减少了约70%。工作温度范围为-40℃至+150℃,与14nm汽车eMRAM相同。写入时间约为200ns,也与14nm一代相同。读出时间小于10ns,比14nm一代的小于15ns短约三分之二。150℃下数据保存期为10年,重写次数为10的6次方。

兼容下一代和 14nm(当前一代)之后的下一代逻辑的车载 eMRAM 技术概述。两者都被假定为用于程序存储的非易失性存储器。摘自三星在 IEDM 2024 上发表的论文

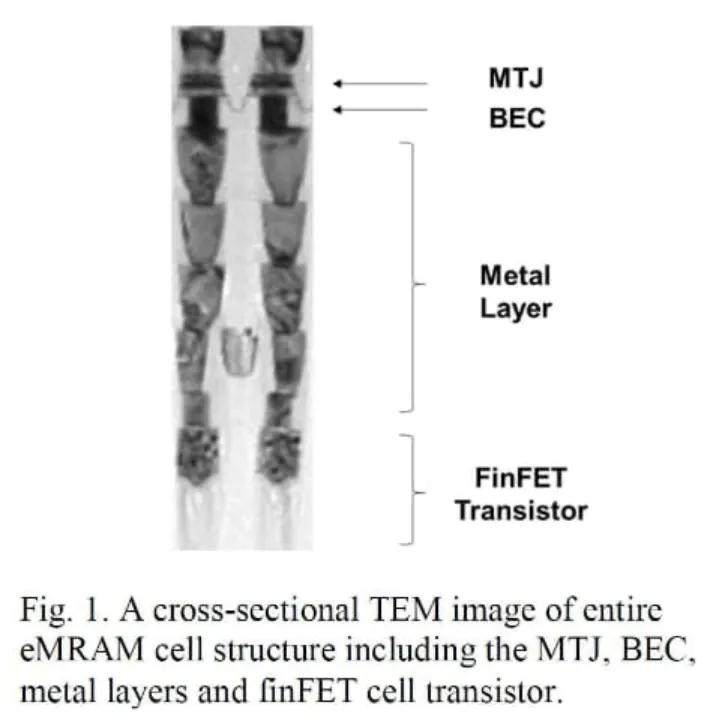

使用 8nm FinFET 逻辑制造技术制作原型的 eMRAM 单元横截面的 TEM 图像。底部电极接触(BEC)和MTJ形成在多层金属布线层上。摘自三星在 IEDM 2024 上发表的论文

逻辑小型化和嵌入式 MRAM 制造良率

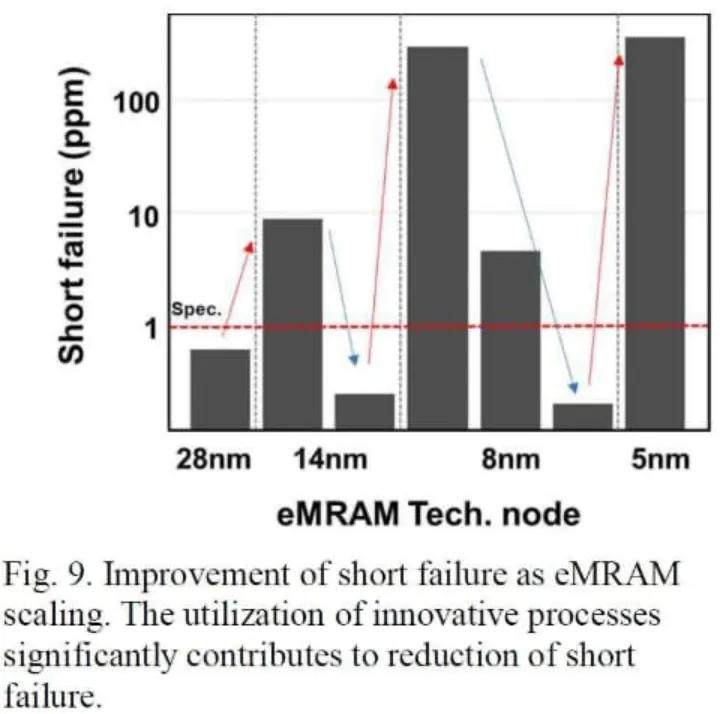

当逻辑制造技术小型化时,MTJ的尺寸和间距通常会减小,导致短路故障导致的故障率急剧增加,这主要是由隧道绝缘膜的介质击穿和异物再沉积造成的。在 MTJ 侧壁上。从这里开始,我们将改进制造工艺,以减少短路缺陷的发生率。一旦缺陷率降低到产品可接受的水平(1 ppm或更低),我们就可以利用缺陷缓解方法(冗余位、纠错等)开始风险生产,并转向全面生产批量生产。

然而,随着逻辑制造技术进一步小型化,MTJ短路故障的数量再次增加。从那时起,与上一代产品一样,制造工艺将得到改进,以减少短路故障的发生率。

逻辑制造技术节点(横轴)与嵌入式MRAM短路故障率(纵轴)的关系。随着技术节点变得更小,短路故障的数量迅速增加。摘自三星在 IEDM 2024 上发表的论文

在8nm节点,通过改进MTJ图案化技术来抑制隧道绝缘膜中针孔的出现,并去除粘附在侧壁上的异物,我们实现了产品级的不良率(1ppm以下)。通过试产,制造良率达到94%(论文中描述为90%,讲座中报道为94%)。

还假设有可能实现支持下一代 5nm 节点 FinFET 逻辑的 eMRAM。存储单元面积预计为0.0011平方微米,比8nm节点小约14%。