文|半导体产业纵横

先进的封装技术和Chiplet要求采用精密且灵活的测试策略。

异构集成正在推动半导体行业的创新,但它也增加了芯片设计的复杂性,需要更为复杂的测试需求。自动测试设备(ATE)行业正在做出响应,开发和使用更精密的测试设备,这些设备能够处理测试异构芯片所需的多样功能和接口。这包括测试不同的通信协议、功率域和热特性,最终使每套集成组件都有自己的参数和性能标准。

异构集成概览

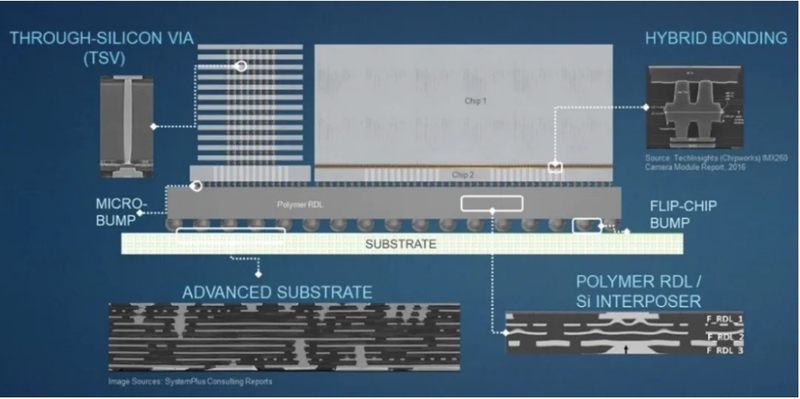

异构芯片,也称为异构集成,涉及将多个单独制造的组件(如处理器、存储器、传感器)组合成一个封装体或系统级封装(SiP)。以这种方式组合的组件,即Chiplet,可以使用不同的工艺和材料制成。图1展示了异构集成的一个版本。

图1:异构集成的一个版本。(来源:应用材料公司)

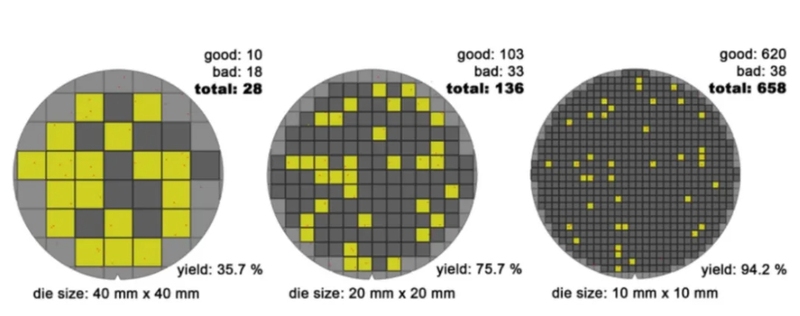

与传统的同质芯片相比,通过利用各种技术和材料,制造商创造出的 SiP 能更高效地执行多种计算任务。系统设计人员可以在更小的空间内获得更高的性能、更低的功耗和更强大的功能。同时,与单片设备相比,Chiplet尺寸更小,可大大提高良品率,从而降低相同设备缺陷密度下的成本,如图 2 所示。这对于AI、5G和IoT等高级应用至关重要,这些应用必须在严格的功耗和空间限制内满足多样化和密集的计算需求。

图2:Chiplet相对于单片设备的较小尺寸使其具有更高的良率。(来源:维基共享资源)

随着技术的不断进步,几乎所有设备都可以根据不同的应用组合成异构封装。因此,测试资源必须能够测试几乎所有类型的功能,同时考虑到从低端到高端的经济性。

对测试行业的全面影响

由于这种增加的复杂性——包括需要更先进的测试设备(如泰瑞达公司的UltraFLEXplus)以及潜在的测试时间延长——优化质量成本至关重要。然而,不同组件之间可能存在相互作用,确保异构芯片的可靠性更具挑战性。

良率管理也变得更加复杂,因为任何组件中的缺陷都可能影响芯片的整体功能。灵活的测试解决方案可能包括专门的测试算法和夹具,以准确评估每个独特芯片的性能和可靠性。

灵活的测试策略必不可少

为了适应先进数字芯片和异构集成的复杂性,行业正在进行一系列测试策略。动态测试覆盖结合了ATE和系统级测试(SLT),在模拟最终使用环境的条件下评估半导体器件。泰瑞达公司的Titan SLT平台就是一个例子,它在需要最高水平系统性能测试的半导体测试环境中提供了灵活性、可扩展性和密度。通过模拟真实世界的场景,动态测试覆盖范围可有效识别故障,否则这些故障可能会被隐藏起来。平衡测试成本和改进故障检测这一策略有助于优化质量成本。此外,它还使制造商能够利用数据分析提高产量,确保只有最高质量的产品进入市场。

左移和右移策略进一步平衡了整个制造流程中的测试覆盖。“左移”策略将测试提前到开发过程的早期,通过更早地发现和解决缺陷来降低整体成本。相反,“右移”策略将测试扩展到后期阶段,包括制造后测试,确保任何潜在缺陷在到达消费者之前都被发现。这些策略共同优化成本、质量和良率。

测试复杂性带来挑战

在2.5D/3D封装中测试已知良好晶粒(KGD)和已知良好中介层(KGI)存在许多必须考虑的挑战。集成是复杂的,3D堆叠中的晶粒和中介层导致多层互连和不同的功能。由于硅通孔(TSV)等错综复杂的连接以及测试探针物理空间的减少,这些元件的小型化增加了难度。

晶粒内的缺陷可能只有在组件集成后才显现。堆叠和键合过程本身可能会引入新的缺陷或加剧现有缺陷,这是由于热应力和机械应力造成的。一旦组件堆叠起来,访问每层进行测试就变得更加困难,需要先进的探测技术和测试访问机制。

高速互连(包括TSV结构)进一步增加了测试的复杂性。TSV(硅通孔)在硅芯片内部提供垂直连接,对于高密度、高性能封装至关重要。然而,其复杂的特性在信号完整性、热管理、制造可变性和测试可访问性方面带来了重大挑战,从而使测试工作变得更加困难。必须对测试设计(DFT)方法进行调整,以适应三维封装测试的特殊要求,确保彻底覆盖故障并最大限度地减少测试逃逸。通过采用内置自测试 (BIST) 结构、扩展边界扫描技术、实施热感知测试、确保缺陷容限以及采用分层测试方法,制造商可以提高先进3D半导体封装的可靠性和性能。

泰瑞达遵循IEEE 1838标准来应对这些挑战,利用其在3D堆叠集成电路中的测试访问架构综合框架。IEEE 1838建立了标准化的测试接口和协议,确保来自不同制造商的不同组件可以使用通用框架进行测试。该标准支持模块化测试访问架构,能够在不同层级和组件间实现可扩展且灵活的测试。基于IEEE 1838准则的BIST电路和DFT功能有助于实现更高的故障覆盖率。为此,泰瑞达的UltraFLEX和UltraFLEXplus以及ETS-88测试仪可为更复杂的器件提供测试能力,提高准确性,降低客户拥有成本。

展望未来,持续创新

半导体行业在不断演进,其驱动力来自对更高性能、更高集成度和更低功耗的需求。对半导体测试产生重大影响的新兴技术包括行业互连标准,如通用小芯片互连快递(UCIe),以及共封装硅光子学的出现。

随着 UCIe 和硅光子技术的发展,互连变得越来越复杂,因此需要先进的测试方法来确保信号完整性和性能。这包括精确鉴定高速信号和严格测试光子元件。

联合封装解决方案需要有效的热管理策略,以防止过热并确保可靠运行。测试必须考虑热效应,并采用热感知测试技术。

随着这些新兴技术的不断发展,半导体行业将受益于更高的性能、更强的集成能力和更高的能效。然而,测试的复杂性也将增加,这就要求测试方法和设备不断创新,以应对这些异构系统带来的独特挑战。测试行业要想走在这些趋势的前面,就要采用标准化的方法和灵活的测试策略确保下一代半导体器件的可靠和高效生产。